# OPTIMIZATION OF PHOSPHORUS EMITTER USING POCI $_3$ DIFFUSION FOR PERC CELLS

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

AHMET EMİN KEÇECİ

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF MASTER OF SCIENCE

IN

MICRO AND NANOTECHNOLOGY

# Approval of the thesis:

## OPTIMIZATION OF PHOSPHORUS EMITTER USING POCI3 DIFFUSION FOR PERC CELLS

submitted by AHMET EMİN KEÇECİ in partial fulfillment of the requirements for the degree of Master of Science in Micro and Nanotechnology, Middle East Technical University by,

| Prof. Dr. Halil Kalıpçılar<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>   |  |

|----------------------------------------------------------------------------------------------|--|

| Prof. Dr. Deniz Üner<br>Head of the Department, <b>Micro and Nanotechnology</b>              |  |

| Prof. Dr. Raşit Turan<br>Supervisor, <b>Micro and Nanotechnology, METU</b>                   |  |

| Assoc. Prof. Dr. Selçuk Yerci<br>Co-Supervisor, <b>Electrical and Electronics Eng., METU</b> |  |

| Examining Committee Members:                                                                 |  |

| Prof. Dr. Hüsnü Emrah Ünalan<br>Metallurgical and Materials Eng, METU                        |  |

| Prof. Dr. Raşit Turan<br>Physics, METU                                                       |  |

| Prof. Dr. Ali Çırpan<br>Chemistry, METU                                                      |  |

| Assoc. Prof. Dr. Mustafa Kulakcı<br>Physics, Eskişehir Technical University                  |  |

| Assist. Prof. Veysel Ünsür<br>Department of Basic Sciences, Necmettin Erbakan Uni.           |  |

Date: 11.05.2023

| I hereby declare that all information in<br>presented in accordance with academic re<br>that, as required by these rules and cond<br>all material and results that are not origin | ules and ethical conduct. I also declare luct, I have fully cited and referenced |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                                                                                                                                                   |                                                                                  |

|                                                                                                                                                                                   | Name Last name : Ahmet Emin Keçeci                                               |

|                                                                                                                                                                                   | Signature:                                                                       |

|                                                                                                                                                                                   |                                                                                  |

|                                                                                                                                                                                   |                                                                                  |

|                                                                                                                                                                                   |                                                                                  |

| iv                                                                                                                                                                                |                                                                                  |

#### **ABSTRACT**

# OPTIMIZATION OF PHOSPHORUS EMITTER USING POCI3 DIFFUSION FOR PERC CELLS

Keçeci, Ahmet Emin Master of Science, Micro and Nanotechnology Supervisor: Prof. Dr. Raşit Turan Co-Supervisor: Assoc. Prof. Dr. Selçuk Yerci

May 2023, 73 pages

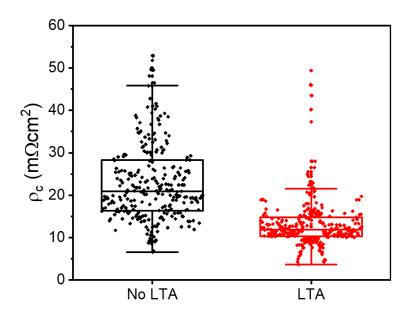

The active dopant profile and the enhanced passivation of the emitter are keys to improving passivated emitter and rear contact (PERC) solar cell efficiency. PERC cells evolved from the standard Al-BSF cells that suffered from recombination losses due to full-area metal contact at the rear side. PERC cell technology enables to reduce the metal contact fraction and considering the total saturation current density ( $J_0$ ), the emitter region has the biggest share. In this work, the optimization of the profile and the passivation of the emitter are investigated. Emitters are formed by using a liquid source phosphoryl chloride (POCl<sub>3</sub>) diffusion process. By varying drive-in conditions, desired profiles can be formed for phosphorus diffused regions. Enhancement in the passivation is observed on the symmetrical emitter samples by using thermally grown silicon dioxide due to its low interface defect density ( $D_{it}$ ). In addition, we show that a low temperature annealing process (LTA) at 700°C for 60 minutes after the silicon nitride ( $SiN_x$ ) deposition improves the surface and the bulk passivation especially for emitters with high surface concentrations ( $\approx 3E20 \text{ cm}^{-3}$ ). According to the results of the symmetrical emitter samples, the saturation current

density of the emitter  $(J_{0,e})$  is reduced from 100 to 60 fA/cm<sup>2</sup> by varying the profile without changing the sheet resistance and below 40 fA/cm<sup>2</sup> by increasing the sheet resistance.

Keywords: liquid source diffusion, emitter, passivation

vi

# PERC TİPİ HÜCRELER İÇİN POCI3 DİFÜZYONU İLE EMİTÖR OPTİMİZASYONU

Keçeci, Ahmet Emin Yüksek Lisans, Mikro ve Nanoteknoloji Tez Yöneticisi: Prof. Dr. Raşit Turan Ortak Tez Yöneticisi: Doç. Dr. Selçuk Yerci

Mayıs 2023, 73 sayfa

Aktif katkı profili ve geliştirilmiş pasivasyon, PERC tipi güneş hücresi verimliliğini iyileştirmenin anahtarıdır. PERC hücreleri, arka taraftaki tam alan metal kontağı nedeniyle rekombinasyon kayıplarından muzdarip olan standart Al-BSF güneş hücrelerinden geliştirilmiştir. PERC hücre teknolojisi, arka taraf metal kontak oranının azaltılmasına olanak sağlar. Toplam doygunluk akım yoğunluğu (J<sub>0</sub>) dikkate alındığında emitör bölgesi en büyük paya sahiptir. Bu çalışmada, profilin optimizasyonu ve emitörün pasivasyonu incelenmiştir. Emitörler, sıvı kaynaklı bir fosforil klorür (POCl<sub>3</sub>) difüzyon işlemi kullanılarak oluşturulmuştur. Sürme koşulları değiştirilerek, fosfor difüzyonlu bölgeler için istenilen profiller oluşturulabilir. Düşük arayüz kusur yoğunluğuna sahip olması nedeniyle termal olarak büyütülmüş silikon dioksitin emitör pasivasyonunu iyileştirdiği simetrik emitör örneklerinde gözlemlenmiştir. Ek olarak, silisyum nitrür (SiN<sub>x</sub>) biriktirme işleminden sonra 700°C'de 1 saat boyunca uygulanan bir tavlama işleminin yüzey ve gövde pasivasyonunu iyileştirdiğini gösteriyoruz. Simetrik emitör örneklerinin sonuçlarına göre, emitör levha direnci değiştirilmeden, profil değiştirilerek emitörün

doyma akım yoğunluğu  $(J_{0,e})$  100'den 60 fA/cm²'ye, levha direnci arttırılarak da 40 fA/cm²'nin altına düşürülmüştür.

Anahtar Kelimeler: sıvı kaynak difüzyon, emitör, pasivasyon

To my family

#### ACKNOWLEDGMENTS

At first, I would like to thank to my advisor Prof. Dr Raşit Turan for accepting me in his team and the opportunities he provides. He has always been encouraging and supportive during my studies.

I would like to share my gratitude with my co-supervisor Assoc. Prof. Dr. Selçuk Yerci and the committee members: Prof. Dr. Hüsnü Emrah Ünalan, Prof. Dr. Ali Çırpan, Assoc. Prof. Dr. Mustafa Kulakcı and Assoc. Prof. Dr. Veysel Ünsür for their time and feedback that carried this work one step further.

I would like to extend my sincere thanks to Dr. E. Hande Çiftpınar and Dr. Gence Bektaş for their supervision, guidance, helps and friendship. They have always been there for me whenever I needed them, they answered all my questions and listened to every problem I have.

Then, I want to share my deepest gratitude to my labmates who contributes to this work: Hasan Hüseyin Canar, Vahdet Özyahni, Sercan Aslan for their fruitful discussion and cooperation during the fabrication and characterization of the samples. I also would like to thank to my former and current colleagues: Dr. Ergi Dönerçark, Dr. Bülent Arıkan, Samet Özdemir, Sümeyye Koçak Bütüner, Hasan Asav, Gamze Kökbudak, Selin Seyrek, Seda Kılıçkaya, Melisa Korkmaz Arslan and Berkay Uygun for their supports in this work. Finally, I am grateful to Elşen Aydın and Gülçin Çelik for their endless support. I am very happy to have them in my life.

I am very grateful to all the technical staff of ODTÜ-GÜNAM, Batuhan Taş, Murat Aynacıoğlu and Furkan Çiçek for their endless support in the technical issues.

And I thank my family for everything and I am grateful to have them.

# TABLE OF CONTENTS

| ABSTRACT                                  | V   |

|-------------------------------------------|-----|

| ÖZ                                        | vii |

| ACKNOWLEDGMENTS                           | x   |

| TABLE OF CONTENTS                         | xi  |

| LIST OF TABLES                            | xiv |

| LIST OF FIGURES                           | xv  |

| CHAPTERS                                  |     |

| 1 INTRODUCTION                            | 1   |

| 1.1 Silicon Solar Cells                   | 2   |

| 1.1.1 Recombination in Emitter            | 3   |

| 1.1.2 Solar Cell Parameters               | 3   |

| 2 LITERATURE REVIEW                       | 7   |

| 2.1 Fundamentals of Diffusion Process     | 7   |

| 2.2 POCl <sub>3</sub> Diffusion Mechanism | 8   |

| 2.2.1 Pre-deposition                      | 8   |

| 2.2.2 Drive-In                            | 10  |

| 2.3 Recombination                         |     |

| 2.3.1 Radiative Recombination             | 14  |

| 2.3.2 Auger Recombination                 | 14  |

|   | 2.3 | .3   | Shockley-Read-Hall Recombination                         | . 15 |

|---|-----|------|----------------------------------------------------------|------|

|   | 2.4 | Lov  | w-Temperature Annealing                                  | .16  |

|   | 2.5 | The  | ermal Oxidation                                          | .17  |

| 3 | FA  | BRI  | CATION OF SOLAR CELL                                     | . 19 |

|   | 3.1 | PEI  | RC Cell Fabrication                                      | . 19 |

|   | 3.1 | .1   | Properties and Fabrication of Si Wafer                   | . 19 |

|   | 3.1 | .2   | Texturing and Cleaning                                   | .20  |

|   | 3.1 | .3   | Doping                                                   | .22  |

|   | 3.1 | .4   | Single Side Etching                                      | .24  |

|   | 3.1 | .5   | Dry Oxidation                                            | .25  |

|   | 3.1 | .6   | Al <sub>2</sub> O <sub>3</sub> Deposition and Activation | .27  |

|   | 3.1 | .7   | ARC and Capping Layer Deposition                         | .29  |

|   | 3.1 | .8   | Laser Ablation for Local Contact Opening                 | .30  |

|   | 3.1 | .9   | Contact Formation                                        | .31  |

|   | 3.2 | Life | etime Samples                                            | .33  |

|   | 3.3 | Me   | asurement Methods                                        | .34  |

|   | 3.3 | .1   | 4-Point-Probe                                            | .34  |

|   | 3.3 | .2   | Electrochemical Capacitance-Voltage                      | .35  |

|   | 3.3 | .3   | Sinton WCT120TS Lifetime Tester                          | .36  |

|   | 3.3 | .4   | Transfer Length Method (TLM)                             | .38  |

|   | 3.3 | .5   | IV Measurement                                           | .39  |

| 1 | RE  | SUL  | TS AND DISCUSSION                                        | .41  |

|   | 4.1 | Opt  | timization of the Process Conditions                     | .41  |

|   | 12  | Ont  | rimization of the Emitter Profile                        | 11   |

| 4.3     | Performance Enhancement of PERC solar cell with SiO <sub>x</sub> N <sub>y</sub> Back | Surface |

|---------|--------------------------------------------------------------------------------------|---------|

| Passiva | ation by LTA Process                                                                 | 51      |

| 4.3.1   | Experimental Details                                                                 | 51      |

| 4.3.2   | 2 Results of the Symmetrical Samples                                                 | 52      |

| 4.3.3   | Results of the PERC Cells                                                            | 55      |

| 4.4     | Emitters with Low Surface Concentration and Deep Junction                            | 56      |

| 5 CON   | NCLUSIONS                                                                            | 67      |

| REFERE  | NCES                                                                                 | 69      |

## LIST OF TABLES

# **TABLES**

| Table 2.1. Recipe parameters and experimental results for recipes at 829°C for a | ıll |

|----------------------------------------------------------------------------------|-----|

| process steps [5]                                                                | 12  |

| Table 4.1. Sheet resistances and doses of the diffused regions before and after  |     |

| annealing with or without PSG layer is on the surface                            | 47  |

| Table 4.2. Properties of the firing recipes                                      | 50  |

| Table 4.3. Properties of PECVD deposited layers                                  | 58  |

| Table 4.4. J <sub>0,e</sub> and τ <sub>bulk</sub> results of emitter P1          | 60  |

| Table 4.5. J <sub>0,e</sub> and τ <sub>bulk</sub> results of emitter P2          | 61  |

# LIST OF FIGURES

# **FIGURES**

| Figure 1.1. The configuration of the PV system from solar cell to grid                        | 2  |

|-----------------------------------------------------------------------------------------------|----|

| Figure 1.2. IV graph of an ideal cell and the cell with series and shunt resistance           | 5  |

| Figure 2.1. Schematic of the wafer after the pre-deposition step of the diffusion             |    |

| process                                                                                       | 9  |

| Figure 2.2. Diffusion mechanism during N <sub>2</sub> drive-in                                | 11 |

| Figure 2.3. Blockage of P diffusion during O <sub>2</sub> drive-in due to a) oxidation of Si  |    |

| interstitials, b) oxidation of free P atoms and c) thick SiO2 interlayer                      | 13 |

| Figure 2.4. Energy band diagram of a) p-type Si, b) n-type Si                                 | 14 |

| Figure 2.5. The schematic of radiative recombination.                                         | 14 |

| Figure 2.6. The schematic of Auger recombination.                                             | 15 |

| Figure 2.7. The schematic of SRH recombination.                                               | 15 |

| Figure 2.8. Effective carrier lifetime of as-deposited and annealed (at 800°C) Si             | Nx |

| films with different gas ratios (R) [11].                                                     | 17 |

| Figure 3.1. SEM images of the surfaces a) as-cut (saw damaged), b) saw damag                  | e  |

| etched and c) random pyramidal textured [21]                                                  | 20 |

| Figure 3.2. Effect of texturing process on light absorption.                                  | 21 |

| Figure 3.3. The schematic of the Si wafer after the texturing process                         | 22 |

| Figure 3.4. The schematic of the gas flows during the pre-deposition process                  | 23 |

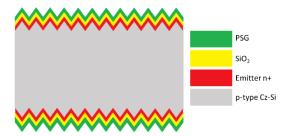

| Figure 3.5. The schematic of the Si wafer after diffusion process                             | 24 |

| Figure 3.6. The schematic of the Si wafer SSE process.                                        | 25 |

| Figure 3.7. The schematic of the dangling bonds at surface [23]                               | 25 |

| Figure 3.8. Qf vs. Dit graph of commonly used dielectric materials in PV                      |    |

| applications [25]                                                                             | 26 |

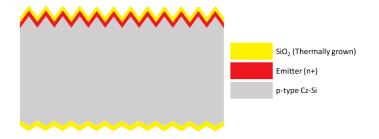

| Figure 3.9. The schematic of the Si wafer after thermal oxidation process                     | 27 |

| Figure 3.10. The schematic of the deposition of stoichiometric Al <sub>2</sub> O <sub>3</sub> | 28 |

| Figure 3.11. The schematic of the Si wafer after Al <sub>2</sub> O <sub>3</sub> deposition    | 28 |

| Figure 3.12. Standard Solar Spectra for space and terrestrial use                             | 29 |

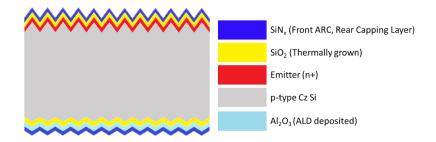

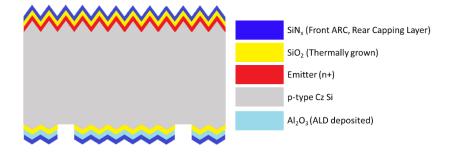

| Figure 3.13. The schematic of the Si wafer after SiNx deposition                                                            | 30 |

|-----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.14. The schematic of the Si wafer after LCO.                                                                       | 31 |

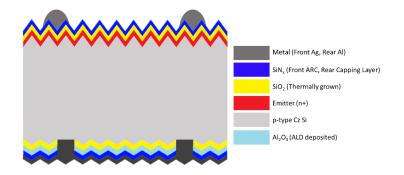

| Figure 3.15. The schematic of the Si wafer after metallization.                                                             | 32 |

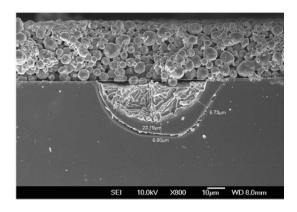

| Figure 3.16. SEM image of the LCO after contact formation [28].                                                             | 32 |

| Figure 3.17. The schematic of the Si solar cell after contact formation                                                     | 33 |

| Figure 3.18. The schematic of the fabrication of symmetrical emitter samples                                                | 34 |

| Figure 3.19. The schematic of 4PP measurement                                                                               | 34 |

| Figure 3.20. The schematic of ECV measurement                                                                               | 36 |

| Figure 3.21. The schematic of Sinton WCT-120TS device                                                                       | 37 |

| Figure 3.22. The schematic of a TLM stripe                                                                                  | 38 |

| Figure 3.23. The schematic of IV measurement.                                                                               | 39 |

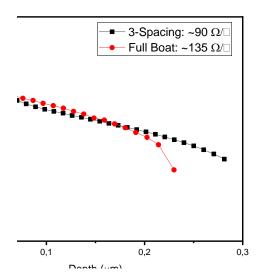

| Figure 4.1. Configuration and positioning of the wafers a) Full-boat b) 3-spacing                                           | 42 |

| Figure 4.2. Active dopant profile of 3-spacing and full-boat configuration of the                                           |    |

| same diffusion recipe                                                                                                       | 43 |

| Figure 4.3. Sheet resistance and non-uniformity values of 3-spacing and full-boat                                           |    |

| configuration of the same diffusion recipe                                                                                  | 43 |

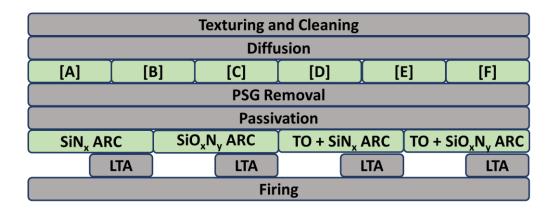

| Figure 4.4. Process flow of the fabricated symmetrical 6 different ([A]-[F]) emitted                                        | er |

| samples                                                                                                                     | 44 |

| Figure 4.5. Process details of recipes                                                                                      | 45 |

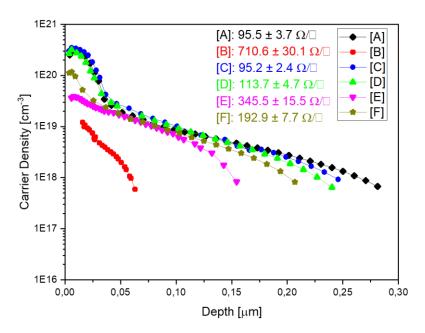

| Figure 4.6. Active dopant profiles of recipes [A]-[F] measured by ECV                                                       | 46 |

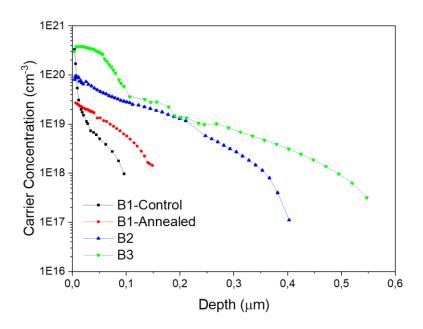

| Figure 4.7. Active dopant profiles of the diffused regions before and after                                                 |    |

| annealing with or without PSG layer is on the surface                                                                       | 48 |

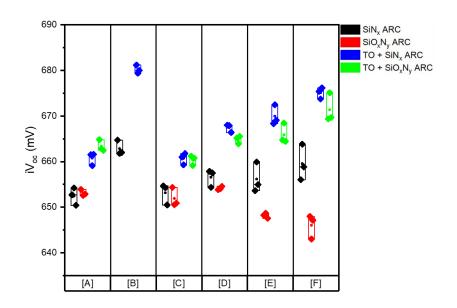

| Figure 4.8. $iV_{oc}$ results of 5 emitters with two different ARCs (SiN <sub>x</sub> and SiO <sub>x</sub> N <sub>y</sub> ) |    |

| and with or without thermal oxide (TO)                                                                                      | 49 |

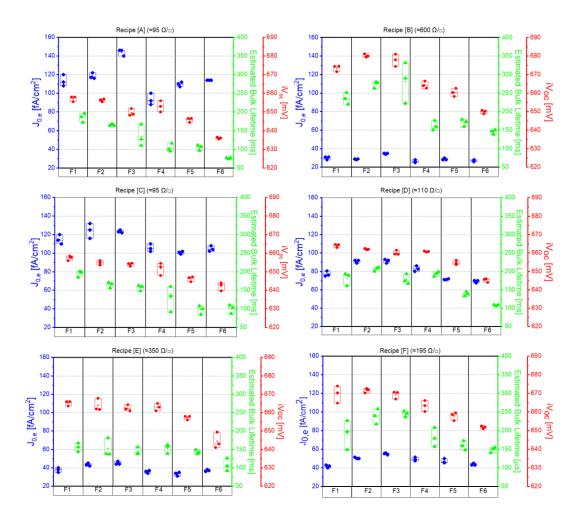

| Figure 4.9. $J_{0,e}$ , estimated bulk lifetime and implied $V_{oc}$ ( $iV_{oc}$ ) results of                               |    |

| symmetrical emitter samples fabricated with 6 different emitter recipes, passivate                                          | d  |

| with SiO <sub>2</sub> /SiNx stack and subjected to different firing temperatures (F1-F6)                                    | 51 |

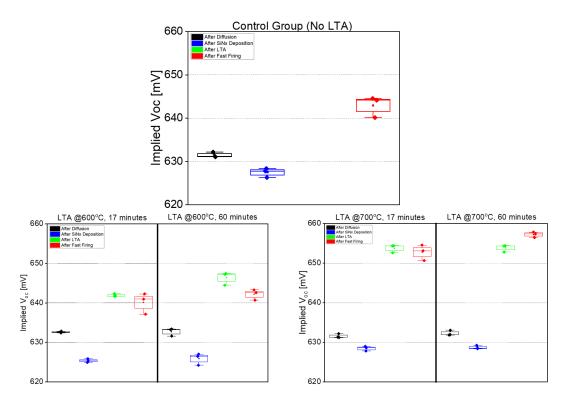

| Figure 4.10. iV <sub>oc</sub> results of the first batch of symmetrical emitter samples with no                             | )  |

| LTA treatment (control group), samples with LTA at 600°C for 17 and 60 minute                                               | es |

| and samples with LTA at 700°C for 17 and 60 minutes                                                                         | 53 |

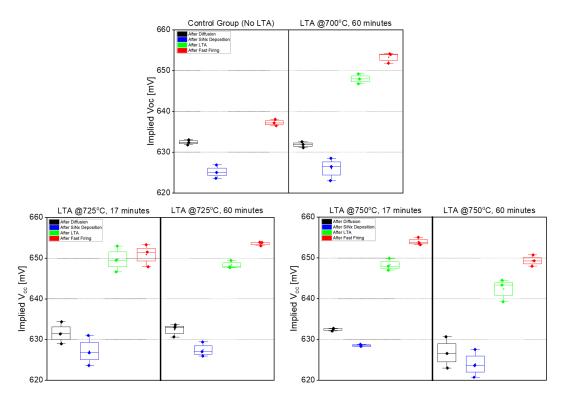

| Figure 4.11. iV <sub>oc</sub> results of the second batch of symmetrical emitter samples with | n    |

|-----------------------------------------------------------------------------------------------|------|

| no LTA treatment (control group) and LTA at 700°C for 60 minutes as a referen                 | ice, |

| samples with LTA at 725°C for 17 and 60 minutes and samples with LTA at 750                   | )°C  |

| for 17 and 60 minutes                                                                         | . 54 |

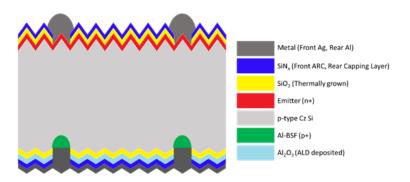

| Figure 4.12. The schematic of the PERC solar cell                                             | . 55 |

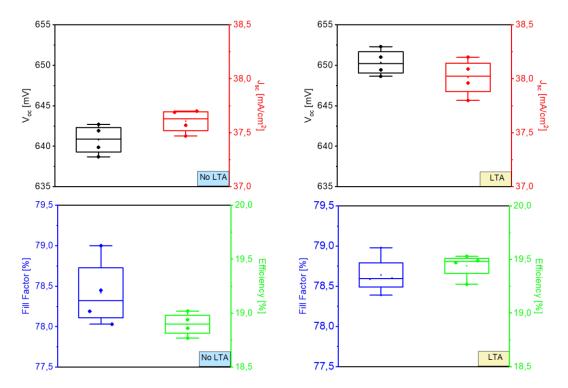

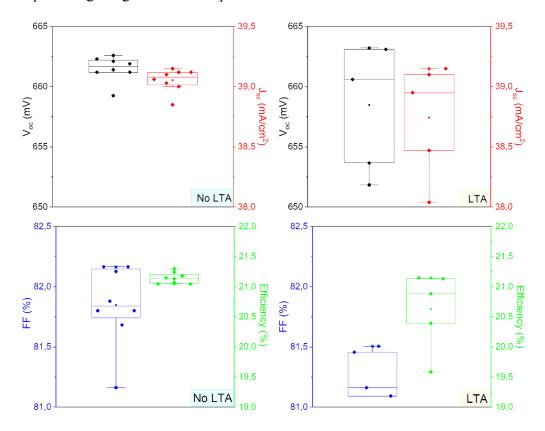

| Figure 4.13. PERC cell results from I-V curve showing the effect of LTA on $V_{oc}$           | ε,   |

| $J_{sc}$ , FF and efficiency on PERC cells fabricated without LTA (left) and PERC ce          | ells |

| fabricated with LTA at 700°C for 60 minutes (right)                                           | . 56 |

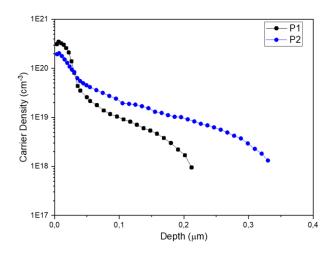

| Figure 4.14 ECV measurement results of recipes P1 and P2                                      | . 57 |

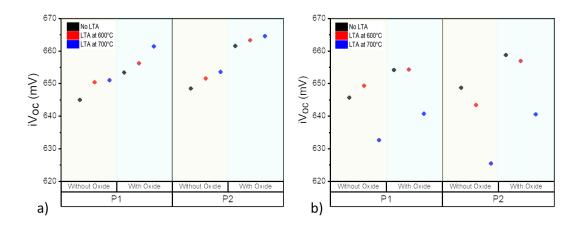

| Figure 4.15. iV <sub>oc</sub> results of symmetrical emitter samples passivated with ARC a)   | ) S1 |

| (SiN <sub>x</sub> stack) b) S2 (SiO <sub>x</sub> N <sub>y</sub> stack)                        | . 58 |

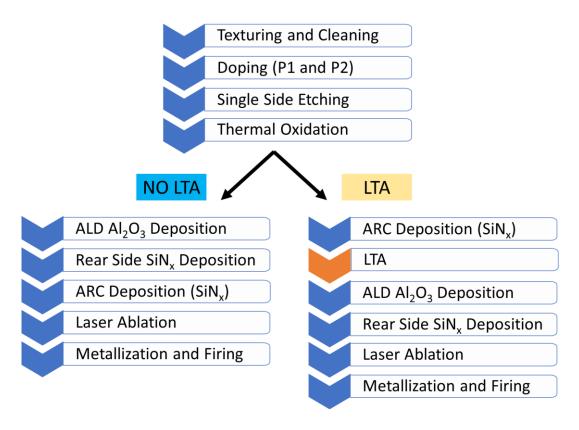

| Figure 4.16. Fabricated PERC cells process flows with and without LTA treatme                 | ent  |

|                                                                                               | . 62 |

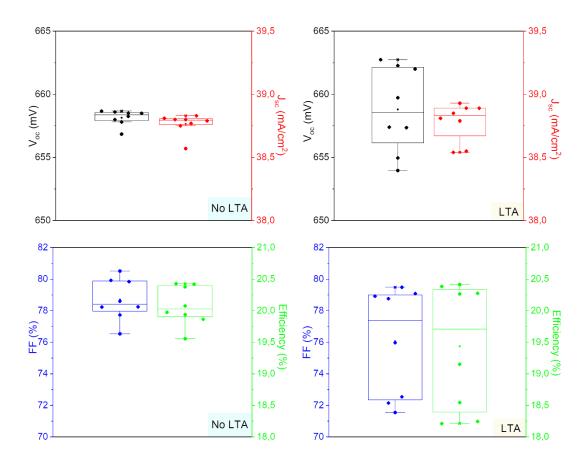

| Figure 4.17. IV results of the PERC cells fabricated with emitter P1                          | . 63 |

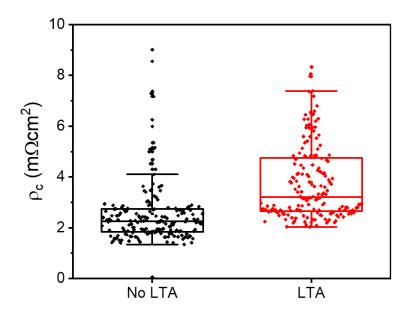

| Figure 4.18. Contact resistivity between Ag paste and emitter P1                              | . 64 |

| Figure 4.19. IV results of the PERC cells fabricated with emitter P2                          | . 65 |

| Figure 4.20. Contact resistivity between Ag paste and emitter P2                              | 66   |

#### **CHAPTER 1**

#### INTRODUCTION

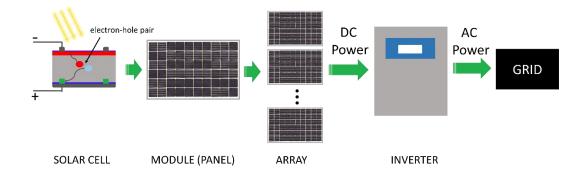

Fossil fuels are carbon-rich materials that can produce electricity by burning. During production, a large amount of CO<sub>2</sub> is emitted. Fossil fuel-fired power plants cause 33%-40% of global CO<sub>2</sub> emissions [1], [2]. CO<sub>2</sub> absorbs sunlight and leads the planet to get hotter. Due to the increase in CO<sub>2</sub> in the atmosphere in the last decades, global warming has become one of the greatest threats to the World. To reduce carbon emissions, renewable energy sources are safe, reliable and low-or-zero carbon footprint alternatives to generate useful energy. Enhancement in the wind, geothermal, biomass, hydro, tidal and solar energy satisfies the important part of this demand. Along with wind energy, solar energy is one of the most popular renewable energy sources. Energy can be generated from sunlight via different applications. Recently, photovoltaics (PV) applications have become favorable due to cost reduction, increased power conversion efficiency (PCE) and longer lifetime of modules. Also, researches show that carbon emission from PV systems is 10 to 53 orders of magnitude lower than oil-fired steam-generating energy systems [3], [4]. In PV, direct current (DC) electricity is generated by a solar cell which is any device that directly converts light energy into electrical energy through the photovoltaic effect. Then, the DC electricity generated by solar cells is converted into alternative current (AC) electricity which the electrical grid uses. The schematic of this conversion is shown in Figure 1.1.

Figure 1.1. The configuration of the PV system from solar cell to grid

#### 1.1 Silicon Solar Cells

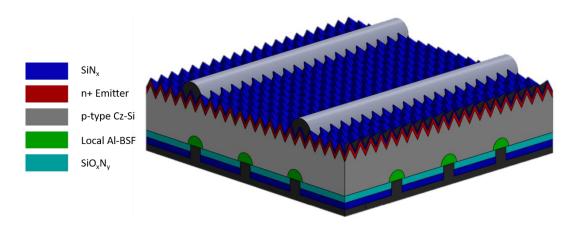

Silicon (Si) based solar cells are the dominant technology in the PV industry because solar cells made from Si provide high efficiency, long lifetime and low cost at the same time. Due to the simplicity and the low cost of production, c-Si homojunction solar cells dominate the PV market. Homojunction is an interface between two similar semiconductor materials with the same band gaps but doped with different materials. In PV, p-type Si wafers doped with boron (B) or n-type Si wafers doped with phosphorus (P) are generally used as bulk materials. Then, to form a homojunction, which is also called as p-n junction, p-type and n-type semiconductor materials are merged. The way to form p-n junction on the p-type or n-type Si wafers is by doping the material with opposite polarity. The capability of processing more than 1000 wafers simultaneously in a single process with high quality makes the liquid source diffusion favorable in industry and research. For passivated emitter and rear contact (PERC) solar cells, p-type Si wafers are used and phosphorus oxychloride (POCl<sub>3</sub>) diffusion is realized to form an n+ emitter region. The amount of resistance and recombination that existed in the device limits the efficiency of a solar cell. Since the standard Al-BSF solar cells are replaced with PERC solar cells; metallized regions, which act as recombination centers, in the solar cells are reduced significantly. Thus, the emitter region has the biggest contribution to the total amount of recombination in the PERC solar cells

#### 1.1.1 Recombination in Emitter

The excess number of dopants in specific regions is one of the major recombination losses. PERC cells have reduced back surface field (BSF) regions compared to standard Al-BSF solar cells. However, the emitter region is similar for both cell types. Considering the total saturation current density, the emitter has the highest contribution in PERC solar cells. Although the metallized areas are more recombinative than passivated emitter regions, the metal fraction is very low compared to passivated areas. Regions in emitter with doping concentrations higher than 1E20 cm<sup>-3</sup> are called as dead layer. Due to high doping concentration in the dead layer, the Auger recombination mechanism becomes dominant and leads to losses in open circuit voltage (V<sub>oc</sub>) and short circuit current (J<sub>sc</sub>). Therefore, an enhancement in the PCE is possible simply by increasing the sheet resistance, i.e., decreasing the amount of dopant, which will reduce the recombination. However, contact resistivity and recombination between the emitter and the metal contacts will increase due to reduced dopants. Developments in the metal pastes enable to get good contact from these emitters with high sheet resistance. Moreover, the selective emitter approach, which is additional doping only under the metal contacts, allows emitters with fewer dopants. Another way to reduce the recombination in the emitter is the enhancement of the passivation layer. By depositing or growing an optimized stack of layers on the emitter, dangling bonds on the surface can be saturated and optimum amount of hydrogen (H) to passivate the bulk and the surface can be provided.

#### 1.1.2 Solar Cell Parameters

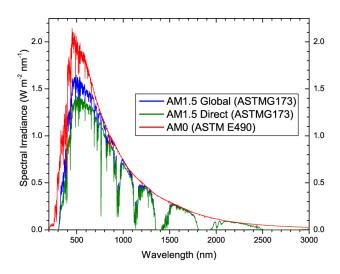

Parameters like  $V_{oc}$ ,  $I_{sc}$  and fill factor (FF) are used to characterize the performance of a solar cell. All these parameters are determined with an IV measurement under standard test conditions (STC). These conditions dictate that solar cells should be measured at 25°C, under 1-sun illumination with a total irradiance of 1000 W/m<sup>2</sup> and the AM1.5 spectrum should be used.

$V_{oc}$  of a solar cell is the maximum voltage available from a solar cell which occurs when no current flows through the external circuit. Voc of a solar cell depends on the light-generated current ( $I_L$ ) and dark saturation current ( $I_0$ ) and the equation when the net current is equal to zero is:

$$V_{oc} = \frac{nkT}{q} ln \left( \frac{I_L}{I_0} + 1 \right)$$

Eq.1

One can expect that increasing temperature also increases the  $V_{oc}$ . However,  $I_0$  depends on the temperature and due to changes in intrinsic carrier concentration  $(n_i)$ ,  $I_0$  increases rapidly.

$I_{sc}$  is the current flows through the external circuit when the electrodes are short-circuited, which means the voltage across the solar cell is zero.  $I_{sc}$  is the maximum current that may be drawn from the solar cell.  $I_{sc}$  depends on the area of the solar cell, the number of photons, the optical properties of the cell (absorption, reflection and transmission) and the spectrum.

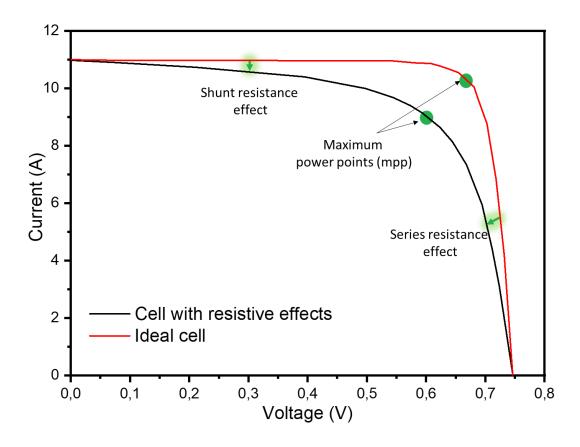

FF is the ratio of maximum power that can be obtained from a solar cell and the product of  $V_{oc}$  and  $J_{sc}$ . For open-circuit and short-circuit conditions, the net power of the solar cell is zero. IV curve of the solar cell is affected by the resistive effects (shunt and series resistance). Series resistance does not affect the  $V_{oc}$  of the solar cell, but series resistance has an impact on the IV curve near the  $V_{oc}$ . On the other hand, shunt resistance strongly affects the IV curve near the  $I_{sc}$ . Figure 1.2 shows an ideal IV curve and IV curve with the effect of series and shunt resistances.

Figure 1.2. IV graph of an ideal cell and the cell with series and shunt resistance

#### **CHAPTER 2**

#### LITERATURE REVIEW

#### 2.1 Fundamentals of Diffusion Process

Diffusion process is commonly used to make Si crystal p-type and n-type, respectively. Using a continuum approach, diffusion process can be well described by Fick's laws. Eq.2 is Fick's first law of diffusion,

$$J = -D \frac{\partial C(x,t)}{\partial x}$$

Eq.2

Where C is the impurity concentration, D is the diffusion coefficient, and J is the net flux of material. The negative sign on the right-hand side of the equation means that the diffusion direction is through decreasing concentration.

Due to the difficulty in detecting the diffusing material, measuring the current density of the impurity is not convenient. Another expression has been developed for that purpose. In Eq.3, measurable quantities are used by assuming a long bar material with a uniform cross-section A, a small volume of length dx. The flux of material entering and leaving the material is shown as  $J_2$  and  $J_1$ , respectively.

$$\frac{J_2 - J_1}{dx} = \frac{\partial J}{\partial x}$$

Eq.3

In the case of unequal  $J_2$  and  $J_1$ , the dopant concentration in the volume must change. In a unit volume, the number of dopants is the product of the concentration and the differential volume element. Thus:

$$\frac{dN}{dt} = Adx \frac{\partial C}{\partial t} = -A(J_2 - J_1) = -Adx \frac{\partial J}{\partial x}$$

Where N is the number of impurities in the volume element, or

$$\frac{\partial C(x,t)}{\partial t} = -\frac{\partial J}{\partial x}$$

Eq.4

By using Fick's first law, Eq.4 can be expressed as:

$$\frac{\partial C(x,t)}{\partial t} = \frac{\partial}{\partial x} \left( D \frac{\partial C}{\partial x} \right)$$

Eq.5

The most common expression of Fick's second law is Eq.5. The interested direction is the z, which is into the wafer and if it is assumed that the diffusion coefficient is independent of position:

$$\frac{\partial C(z,t)}{\partial t} = D \frac{\partial^2 C(z,t)}{\partial z^2}$$

Eq.6

Finally, in three dimensions for an isotropic medium, Fick's second law is expressed as:

$$\frac{\partial c}{\partial t} = D\nabla^2 C$$

Eq.7

#### 2.2 POCl<sub>3</sub> Diffusion Mechanism

For P doping, the chemical POCl<sub>3</sub> is used in the liquid form. In section 3.1.3, it is explained how POCl<sub>3</sub>,  $N_2$  and  $O_2$  are supplied into the tube furnace. In this section, a detailed explanation of the mechanism of POCl<sub>3</sub> diffusion will be given.

#### 2.2.1 Pre-deposition

$$4POCl_3 + 3O_2 \rightarrow 2P_2O_5 + 6Cl_2$$

Eq.8

During the pre-deposition step, at the inlet of the tube furnace, N<sub>2</sub> carried POCl<sub>3</sub> and O<sub>2</sub> meets. At high temperatures, POCl<sub>3</sub> decomposes and the reaction defined by Eq.8 is realized [5]. Phosphorus oxide (P<sub>2</sub>O<sub>5</sub>) is one of the products of the reaction and

carries P atoms to the surface of the Si wafer. Chlorine (Cl<sub>2</sub>) leaves the system without involving any reaction.

$$Si + O_2 \rightarrow SiO_2$$

Eq.9

$$SiO_2 + P_2O_5 \rightarrow SiO_2.P_2O_5$$

Eq.10

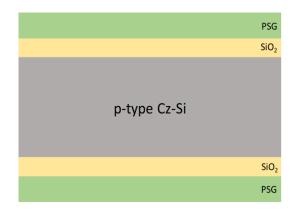

While the reaction in Eq.8 is continuously realized, the reaction in Eq.9 is also occurred. SiO<sub>2</sub> is formed at the surface of the Si wafer by the reaction of Si interstitials and O<sub>2</sub>. After that, P<sub>2</sub>O<sub>5</sub> reaches the Si wafer surface and PSG is formed as a product of the reaction in Eq.10. Composition of the PSG may vary with the process parameters, especially changes in the ratio of POCl<sub>3</sub>/O<sub>2</sub> during the predeposition.

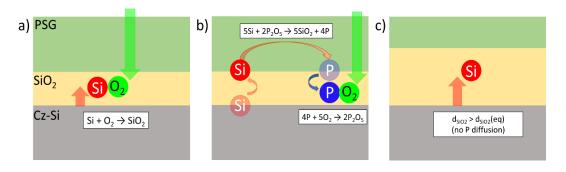

$$5Si + 2P_2O_5 \rightarrow 5SiO_2 + 4P$$

Eq.11

At this point, PSG is formed on the Si wafer, and a SiO<sub>2</sub> layer still exists between PSG and Si surface. In Figure 2.1, the current structure after the pre-deposition step is illustrated. While the POCl<sub>3</sub>, O<sub>2</sub> and N<sub>2</sub> gas flows are active and chemical reactions in Eq.8, Eq.9 and Eq.10 are occurred, Si interstitials start to move from the Si wafer to the PSG layer through the SiO<sub>2</sub> layer. When they reach the PSG layer, the chemical reaction in Eq.11 takes place and free P atoms are released. These free P atoms move from PSG to the Si surface through the SiO<sub>2</sub> layer and diffuse into the wafer.

Figure 2.1. Schematic of the wafer after the pre-deposition step of the diffusion process.

#### 2.2.2 Drive-In

After the pre-deposition step, desired PSG is formed and this layer acts as an infinite source. During the pre-deposition step, a certain amount of P atoms is diffused into the Si wafer. A drive-in process generally in higher temperatures is introduced after the pre-deposition step to send more P atoms into bulk further and obtain a deeper profile. Depending on the temperature, time and ambient conditions, the profile of the diffused regions changes. The drive-in step can be divided into two categories.

#### 2.2.2.1 N<sub>2</sub> Drive-In

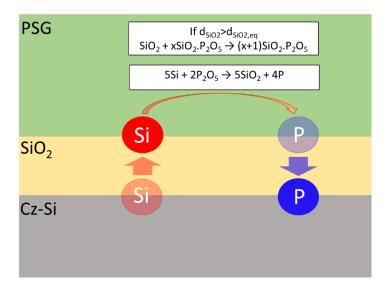

$N_2$  is an inert gas under tube furnace conditions. This implies that  $N_2$  ambient does not cause a direct change in the PSG and Si wafer. POCl<sub>3</sub> carried by  $N_2$  and  $O_2$  gas flows are closed. Therefore, unlike reactions in Eq.11 and Eq.12; Eq.8, Eq.9 and Eq.10 are inactive during  $N_2$  drive-in. In Eq.11, Si interstitials react with  $P_2O_5$  in the PSG and form  $SiO_2$  and free P atoms, which diffuse from PSG to the Si wafer. Also, the reaction in Eq.12 is realized and excess  $SiO_2$  dissolves in the PSG layer.

$$SiO_2 + xSiO_2.P_2O_5 \rightarrow (x+1)SiO_2.P_2O_5$$

Eq.12

Jäger et al. have shown a temperature-dependent equilibrium SiO<sub>2</sub> thickness for drive-in under N<sub>2</sub> ambient [5]. They propose that these two reactions are in a dynamic balance when the equilibrium thickness is reached. Suppose the SiO<sub>2</sub> thickness is bigger than the equilibrium thickness. In that case, excess SiO<sub>2</sub> will be dissolved in the PSG or if the SiO<sub>2</sub> thickness is smaller than the equilibrium, then the reaction in Eq.11 will be dominant and growth of the SiO<sub>2</sub> will be observed until it reaches equilibrium thickness. These mechanisms are shown in Figure 2.2.

Figure 2.2. Diffusion mechanism during N<sub>2</sub> drive-in

Under N<sub>2</sub> ambient, if the SiO<sub>2</sub> thickness is equal to or lower than the equilibrium thickness, P will be continuously transitioned from PSG to Si wafer. Increasing the process temperature will increase P diffusivity and more P atoms will diffuse into the Si wafer [5], [6]. Also, by increasing the duration of the drive-in step, more P atoms will be allowed to diffuse even if the temperature is the same.

#### 2.2.2.2 O<sub>2</sub> Drive-In

In Eq.9 and Eq.13, O<sub>2</sub> oxidizes the Si and P, respectively. If there is a flow of oxygen during the drive-in, it will affect P diffusion into the Si wafer or Si interstitial diffusion from the Si wafer to PSG. Several ideas have been proposed to explain how drive-in under O<sub>2</sub> ambient suppresses the P diffusion from PSG to Si wafer. Werner et al. have shown that a drive-in step under an ambient containing 100% O<sub>2</sub> increases the SiO<sub>2</sub> thickness [7]. For a diffusion process with 10 and 60 minutes of drive-in steps under O<sub>2</sub> ambient, almost the same amount of P diffuses into the Si wafer. Therefore, they claim that if the SiO<sub>2</sub> thickness exceeds a critical point, it will block P diffusion into the Si. On the other hand, Li et al. reported that SiO<sub>2</sub> thickness is independent of the process conditions and this intermediate SiO<sub>2</sub> thickness is around 5.5 nm [8]. Also, since the SiO<sub>2</sub> thickness is the same for all cases, they claim that

blockage of the P diffusion into Si is due to the reaction in Eq.13, which is the oxidation of free P atoms.

$$5O_2 + 4P \rightarrow 2P_2O_5$$

Eq.13

Finally, a comprehensive study by Jäger et al. showed that the main mechanism of restraining P diffusion during drive-in under O<sub>2</sub> ambient is the oxidation of Si interstitial diffuses from Si wafer to PSG [5].

Table 2.1. Recipe parameters and experimental results for recipes at 829°C for all process steps [5]

| Recipe | Temperature | Drive-In | Drive-In | Thickness           | RSheet             | NSurface    |

|--------|-------------|----------|----------|---------------------|--------------------|-------------|

|        | [°C]        | $O_2$    | $N_2$    | of SiO <sub>2</sub> | $[\Omega/\square]$ | $[cm^{-3}]$ |

|        |             | [min]    | [min]    | [nm]                |                    |             |

| A1     | 829         | 0        | 0        | $2.8 \pm 0.5$       | $455 \pm 138$      | 2E19        |

| A2     | 829         | 5        | 0        | $1.8 \pm 0.5$       | $481 \pm 152$      | 1E19        |

| A3     | 829         | 20       | 0        | $2.8\pm0.5$         | $502 \pm 150$      | 1E19        |

| A4     | 829         | 60       | 0        | $6.9 \pm 0.5$       | $510 \pm 126$      | 1E19        |

| A5     | 829         | 120      | 0        | $10.3 \pm 0.5$      | $515 \pm 63$       | 1E19        |

| A6     | 829         | 0        | 120      | $4.8\pm0.5$         | $65 \pm 2$         | 3E20        |

| A7     | 829         | 5        | 115      | $4.9\pm0.5$         | $75 \pm 2$         | 3E20        |

| A8     | 829         | 20       | 100      | $4.6 \pm 0.5$       | $153 \pm 6$        | 2E20        |

| A9     | 829         | 60       | 60       | $4.9 \pm 0.5$       | $548 \pm 138$      | 1E19        |

|        |             |          |          |                     |                    |             |

In Table 2.1, the recipes and the results they obtained are given. From recipe A1 to A5, although the drive-in under O<sub>2</sub> ambient duration increases, the diffused regions' sheet resistance and surface concentration are similar. Figure 2.3.a and Figure 2.3.b illustrate that during the drive-in, P diffusion is blocked due to the oxidation of Si interstitials and probably the free P atoms on the atomic scale even if the SiO<sub>2</sub> thickness is lower than the equilibrium thickness. However, O<sub>2</sub> is not the only restricting mechanism of P diffusion into Si as it is illustrated in Figure 2.3.c. If the

SiO<sub>2</sub> thickness is larger than the equilibrium thickness, the Si interstitials cannot reach the PSG layer and form free P atoms. This situation is observed in recipe A9. When recipes A5 and A9 are compared, the same sheet resistances and surface concentrations are seen for both recipes. An additional drive-in under N<sub>2</sub> for recipe A9 does not change the results because of the thick SiO<sub>2</sub> layer grown during the first drive-in step under O<sub>2</sub> for 60 minutes.

Figure 2.3. Blockage of P diffusion during O<sub>2</sub> drive-in due to a) oxidation of Si interstitials, b) oxidation of free P atoms and c) thick SiO<sub>2</sub> interlayer

#### 2.3 Recombination

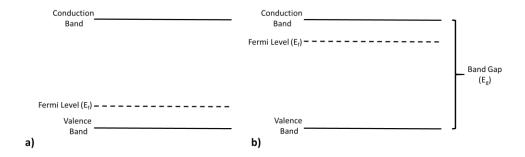

In Figure 2.4, the energy band diagram of the Si semiconductor is shown. When the semiconductor absorbs light, the electron in the valence band is excited to the conduction band and leaves a hole behind at the valence band, which acts as a positively charged particle. This excited electron and the empty space in the valence band are called as electron-hole pair. A certain amount of time passes before the electron loses energy and recombines with the hole. The duration between the excitation and recombination is called as minority carrier lifetime ( $\tau_n$  or  $\tau_p$ ). The lifetime of the carriers depends on how many recombination active sites exist at the surface or bulk of the semiconductor. There are three types of recombination in single-crystal semiconductors: radiative, Auger and Shockley-Read-Hall (SRH).

Figure 2.4. Energy band diagram of a) p-type Si, b) n-type Si

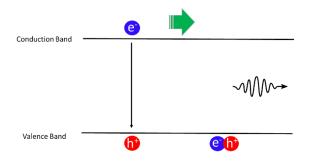

#### 2.3.1 Radiative Recombination

The radiation recombination, which is also called band-to-band recombination, is the the inverse of electron excitation. Electron combines with the hole and emits a photon with an energy similar to the Si bandgap. This type of recombination is not a dominant mechanism in Si solar cells because Si is an indirect bandgap material. The schematic of the radiative recombination is shown in Figure 2.5.

Figure 2.5. The schematic of radiative recombination.

#### 2.3.2 Auger Recombination

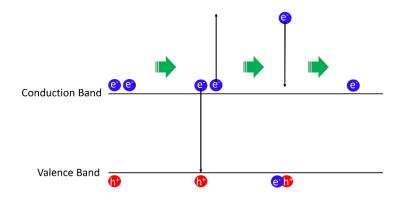

Auger recombination is caused mainly due to the high dopant concentration or injection level. In the emitter, a region so-called dead layer, which has a dopant concentration above 1E20 cm<sup>-3</sup>, suffers from this type of recombination. Three charge carriers are involved. Excess energy is transferred into an electron (eeh

process) or hole (ehh process). This electron and hole then thermalize back down to its original band edge. The schematic of the Auger recombination is shown in Figure 2.6.

Figure 2.6. The schematic of Auger recombination.

#### 2.3.3 Shockley-Read-Hall Recombination

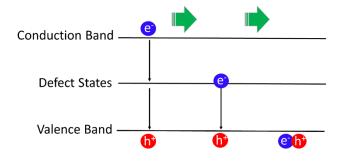

Defect and trap levels in the band gap of the semiconductor mainly cause Shockley-Read-Hall (SRH) recombination. Inorganic and organic impurities are introduced in bulk intentionally (doping) or unintentionally during crystal growth and fabrication processes. First, electrons in the conduction band release energy and drops to an extra level in the forbidden gap. Then, electrons release more energy, drop the valence band, and recombine with holes. The schematic of the SRH recombination is shown in Figure 2.7.

Figure 2.7. The schematic of SRH recombination.

### 2.4 Low-Temperature Annealing

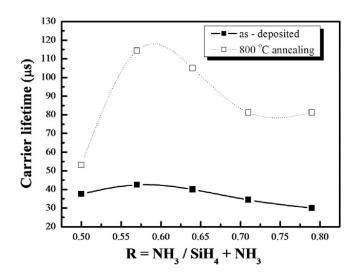

Low-temperature annealing (LTA) is a process of annealing the emitter before or after the SiN<sub>x</sub> deposition. LTA can be performed with a rapid thermal processing (RTP) tool for a very short time or in a tube furnace for a long time. The process is called as LTA because the annealing does not affect the active P concentration, which means the temperature is below the diffusion temperature. According to Shirazi et al., the LTA process dissolves electrically inactive P in the emitter, which is formed due to the rapid cooling down at the end of the diffusion process [9]. They demonstrated that depending on the inactive P in the emitter, reductions in the saturation current density of the emitter  $(J_{0,e})$  are observed without any significant changes in the sheet resistance. In addition, it is known that the right amount of H in bulk and the surface helps to increase the passivation. However, an excess amount of H or lack of H causes deterioration of passivation. During the LTA process  $(\geq 400^{\circ}\text{C})$  after SiN<sub>x</sub> deposition, H in the SiN<sub>x</sub> layer is released [10]. J. Yoo et al. suggest that there is an optimized condition for the gas ratio of (NH3)/(SiH4+NH3) and annealing temperature to be maintained to obtain the highest lifetime values [11]. In Figure 2.8, for an annealing temperature of 800°C, the gas ratio is found to be 0.57.

Figure 2.8. Effective carrier lifetime of as-deposited and annealed (at 800°C) SiNx films with different gas ratios (R) [11].

At an optimized condition, Sharma et al. show that by applying an LTA process, higher  $V_{oc}$  and  $J_{sc}$  values on n-PERT solar cells are obtained [12]. Also, the FF of the cell can be increased due to the passivation of crystallographic defects and gettering of metal impurities on the cast-mono crystalline wafers by an LTA treatment [13]. In addition, C. Sen et al. demonstrate that a pre-firing annealing process helps suppress light and elevated temperature-induced degradation (LeTID) on p-type mc-Si wafers [14]. They show that the degradation at the maximum degradation point, 40% less degradation, is observed for the annealed samples.

#### 2.5 Thermal Oxidation

Thermal oxidation is one of the techniques that is used for passivating the Si surface with  $SiO_2$ . The main difference is that an oxidizing agent diffuses and reacts with the material itself. In the case of Si,  $O_2$  diffuses and reacts with the Si atoms. Since Si atoms in bulk are bonded, it is impossible to grow  $SiO_2$  in two lateral directions. The only way is to grow outside of the wafer. Si can be thermally oxidized by dry  $O_2$  or water vapor (wet oxidation) by reactions shown in Eq.14 and Eq.15, respectively.

The oxidation rate is much higher with water vapor, so it is preferred to grow  $SiO_2$  films thicker than 0.2  $\mu$ m [15].

$$Si + H_2O \rightarrow SiO_2 + H_2$$

Eq.14

$$Si + O_2 \rightarrow SiO_2$$

Eq.15

Wet oxidation is preferred to grow thick SiO<sub>2</sub> films, but due to the fast oxidation, more dangling bonds are left unsaturated, which behave as recombination centers. Dry oxide is denser, cleaner and more controlled than wet oxide and saturates the dangling bonds at the Si surface better [16]. In this study, the passivation of the Si surface is the key goal. Thus, the thin dry oxide is enough the saturate the dangling bond at the surface.

The deal-Grove model describes the kinetics of the growth mechanism [deal-grove-ref]. According to the model, the required time  $(\tau)$  for growing an oxide with a certain thickness  $(x_{ox})$  on a bare Si surface at a constant temperature is:

$$\tau = \frac{x_{ox}}{B/A} + \frac{x_{ox}^2}{B}$$

Eq.16

where the constants A and B relate to the properties of the reaction and the oxide layer, respectively.

#### **CHAPTER 3**

#### FABRICATION OF SOLAR CELL

## 3.1 PERC Cell Fabrication

To observe the real performance of the optimized emitters, PERC solar cells are fabricated in this study. In this section, details about the process flows are described.

## 3.1.1 Properties and Fabrication of Si Wafer

PERC cells are currently the dominant cell structure in the PV market due to their high efficiency, low cost and simplicity in fabrication. P-type (B-doped) Czochralski-grown Si wafers (Cz-Si) are preferred since the segregation coefficient (k<sub>0</sub>) of B is 0.8, which means that a slight change in the resistivity throughout the ingot is observed [17]. To fabricate p-type wafers, B is usually used as a base dopant. However, in the case of gallium (Ga), the segregation coefficient is 0.008 [18], so significant changes in the ingot are observed and industrial point of view; this is not a desirable situation. Moreover, by comparing with n-type wafers, B-doped p-type wafers have the advantage of low cost. However, B-doped p-type wafers suffer from light-induced degradation (LID) due to boron-oxygen (BO) complexes and light and elevated temperature-induced degradation (LeTID). Also, they are sensitive to metallic impurities more than n-type wafers. It is possible to partially eliminate LID, LeTID and metallic impurities by a gettering process like phosphorus diffusion [19], [20]. After the growth of the Si ingot, a wire saw is used to slice ingot into wafers.

# 3.1.2 Texturing and Cleaning

After Si ingots are grown, they are sliced into Si wafers with a thickness of around 180-200 µm by a wire saw. Due to the nature of the process, saw damages on the surface exist and the resulting surface is reflective. The wafers at this stage are called-as as-cut wafers. To remove saw damages and absorb more light, the surface structuring process so-called texturing is applied.

Figure 3.1. SEM images of the surfaces a) as-cut (saw damaged), b) saw damage etched and c) random pyramidal textured [21]

In Figure 3.1.a, scanning electron microscopy (SEM) image of a saw damage surface is shown. When slicing ingots into wafers, the surface becomes rough and contains impurities. In ODTU-GÜNAM Photovoltaic Line (GPVL), surface structuring is done by the RENA Batchtex device. First, as-cut wafers go into a bath with a mixture of DI Water and KOH. Saw damages due to the slicing process are removed with a diluted KOH solution. These saw-damaged removed wafers are called as saw damage etched (SDE) wafers and the surface of the wafers are nearly polished which is shown in Figure 3.1.b. After saw damage removal process, the wafers go into the process bath. This bath contains a mixture of deionized (DI) water, KOH and monoTEX additive. The process is based on the difference in etch rate between the faces. Etch rate of {100} and {110} faces are much higher than {111} face. Due to this difference, the pyramidal shape is formed on the surface, as illustrated in Figure 3.1.c.

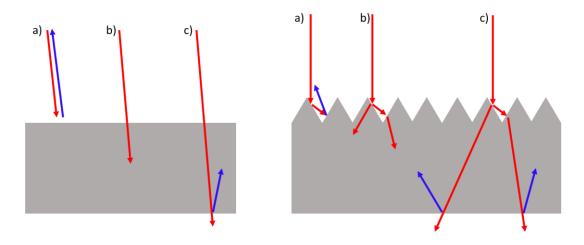

Figure 3.2 explains the logic behind this type of surface structuring. When the light arrives at the surface, there are two options: Absorb or reflect. In the case a), the light is reflected. If the surface is polished, as in SDE wafers, the light has only one chance to get absorbed by the wafer. If the surface is textured, the light can also reflect, but now it has a second chance of getting absorbed by the wafer. The texturing process can reduce the amount of reflection from ~30% to ~10%. In the case b), light is absorbed by the wafer. Finally, in the case c), the light is either transmitted or reflected at the rear surface. High energy photons are absorbed easily in the Si bulk closer to the front surface. However, low-energy photons get absorbed closer to the rear surface. Therefore, if the light is not absorbed, it can be reflected back at the rear surface and had another opportunity to be absorbed by the Si. Textured surface changes the light's direction and when it reaches the back surface, it is not perpendicular. So, the light can be reflected back into Si [22].

Figure 3.2. Effect of texturing process on light absorption.

After the texturing process, the O<sub>3</sub> cleaning process is realized in another bath to remove inorganic and organic impurities on the wafers. A thin ozone-oxide layer is grown on the wafers' surface, so a small amount of Si is also removed. To remove the undesired ozone-oxide layer, wafers go into an HF bath. After rinsing the wafers in deionized water (DI water) and drying them in a hot N<sub>2</sub> environment, the wafers are ready for the doping process. The final structure at the end of the texturing process is shown in Figure 3.3.

Figure 3.3. The schematic of the Si wafer after the texturing process.

# **3.1.3 Doping**

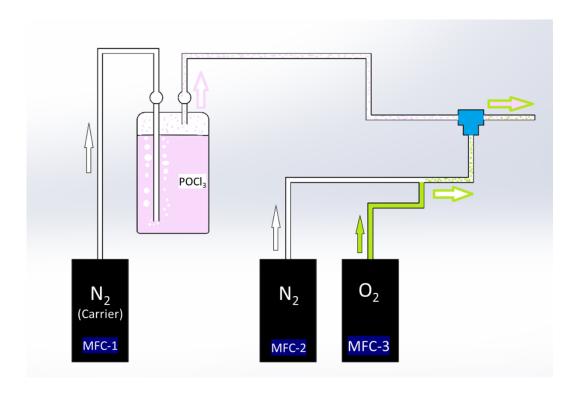

The light excites an electron from the valence band to the conduction band when absorbed by the semiconductor and an electron-hole pair is created. If these electronhole pairs are not separated by a junction and collected after, the electron loses energy and recombines. By doing so, electrons generate heat or light depending on the semiconductor's bandgap structure. In photovoltaics, it is desired to separate and collect electron-hole pairs effectively to generate electricity. To do that, a p-n junction is introduced in the device to create an embedded electric field. In the absence of a junction, carriers do not have a defined direction, so they move a certain distance at a constant velocity but in a random direction [23]. In the presence of a pn junction, due to drift current, carriers have a net direction depending on the charge of the carrier. In PERC cells, B-doped p-type wafers are used. Therefore, the n+ emitter region is formed on the front side of the wafer to create a p-n junction mostly either by POCl<sub>3</sub> diffusion, P ion implantation, PH<sub>3</sub> Diffusion or atmospheric pressured chemical vapor deposition (APCVD) deposited PSG. In ODTÜ-GÜNAM, atmospheric pressure POCl<sub>3</sub> diffusion is used due to the low costs, good stability, relative simplicity, and high throughput of the available production equipment [24]. Figure 3.4 shows the schematic of the process gas flows during the pre-deposition process. There are three mass flow controllers (MFC). MFC-1 controls the flow of N<sub>2</sub> carrier gas flow in the bubblers, while MFC-2 controls the flow of N<sub>2</sub>, which is used for the carrier gas stream in the furnace. MFC-3 controls the O<sub>2</sub> flow, which is necessary for pre-deposition and drive-in steps. The gases from MFC-2 and MFC-3

are joined right after they leave MFCs. On the other hand, N<sub>2</sub> carrier gas flow from MFC-1 goes through the POCl<sub>3</sub> bubbler and N<sub>2</sub>/POCl<sub>3</sub> mixture is come out of the bottle. Then, right before the furnace's inlet, the MFC-2 and MFC-3 are joined with the gas flow left from the POCl<sub>3</sub> bubbler.

Figure 3.4. The schematic of the gas flows during the pre-deposition process.

To load the Si wafers into the diffusion furnace, a diffusion boat with 270 slots is used. Schematics of the boat and loaded wafers are shown later in section 4.1. After wafers are loaded into the boat and sent into the tube, the temperature is ramped up to pre-deposition conditions. O<sub>2</sub>, N<sub>2</sub>, and carrier N<sub>2</sub> gas flows are active during the pre-deposition. During this step, P<sub>2</sub>O<sub>5</sub> is formed due to the reaction of POCl<sub>3</sub> and O<sub>2</sub>. Then, this P<sub>2</sub>O<sub>5</sub> reacts with the SiO<sub>2</sub> on the Si surface and forms PSG, which acts as an infinite P source. At the end of the pre-deposition, the temperature is ramped up to the drive-in conditions. During the ramp-up and drive-in steps, the N<sub>2</sub> flow is always active, but depending on the application, O<sub>2</sub> flow is either active or not. Then, the temperature decreases to a temperature lower than 800°C and the samples are

removed from the furnace. More detailed information, literature reviews and chemical mechanism of the process were given in section 2.2. The current structure after the diffusion process is shown in Figure 3.5.

Figure 3.5. The schematic of the Si wafer after diffusion process.

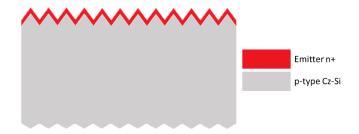

## 3.1.4 Single Side Etching

The formation of the p-n junction is done by the POCl<sub>3</sub> diffusion process. However, as seen in Figure 3.5, both the front and rear surfaces have a diffused region. Electrons are collected at the n+ emitter region and holes from the p-type bulk region. If the emitter and bulk regions are not isolated, an alternative way for the electrons will exist and reduce the shunt resistance of the device. Thus, the FF of the cell will be decreased, which will cause low PCE. A single-side etching (SSE) process is applied to the wafers right after the diffusion process to overcome this problem. In addition, at the end of this process, the rear surface morphology is also changed. While etching the phosphorus diffused region from the rear side, the surface is polished in the process bath. Polish surface has higher electrical performance due to reduced surface area. It also has higher reflection than a textured surface which is necessary for back reflection of the non-absorbed light. This polishing increases the IR response of the device.

RENA Inpilot device is used for the SSE process. After the diffusion process, the samples are put on the device's rollers. The rollers turn and move the wafers from one bath to another. The main goal of the process is to protect the front side while the rear side of the wafers is etched and polished. In the process bath, the wafers' rear side is etched with the mixture of HNO<sub>3</sub>/HF/H<sub>2</sub>SO<sub>4</sub>, while the front side is protected

with DI water. The final structure at the end of the SSE process is given in Figure 3.6.

Figure 3.6. The schematic of the Si wafer SSE process.

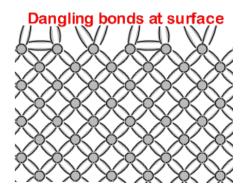

# 3.1.5 Dry Oxidation

The proper structure is formed on the Si wafers at the end of the SSE process. Emitter and bulk regions are isolated with a p-n junction and the electrons and holes can be separated effectively. However, preventing electron-hole pairs from recombination is now the primary concern. There are many reasons to cause recombination in solar cells. P diffused emitter is a highly recombinative region due to a high amount of dopant which causes Auger recombination. Also, because of the impurities and defects in the bulk and emitter, SRH recombination exists. Moreover, the surfaces of both sides of the wafer are highly recombinative regions due to dangling bonds.

Figure 3.7. The schematic of the dangling bonds at surface [23]

In Figure 3.7, the crystal structure of a Si wafer is shown. At the surface, Si atoms have dangling bonds accepted as recombination centers. To saturate these bonds, surfaces should be passivated with dielectric layers. These layers should have the

capability to saturate the bonds at the surface, should not absorb any photon in the solar spectrum and should not create inversion at the surface.

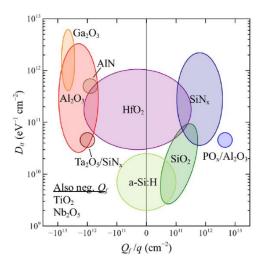

Figure 3.8. Qf vs. Dit graph of commonly used dielectric materials in PV applications [25].

In Figure 3.8, some dielectric materials are shown. Generally, low interface defect density ( $D_{it}$ ) and high fixed charge density ( $Q_f$ ) are desired depending on the surface type and application. Thermally grown  $SiO_2$  has already been shown as a good chemical passivator and has positive fixed charges, but the fixed charge density of the  $SiO_2$  is low [26]. Also, it grows on both sides of the wafers. Low  $D_{it}$  of the layer is desired, but low positive fixed charge density does not exactly satisfy the requirements for both sides. Therefore, a low-temperature oxidation is applied after the SSE process to grow a very thin layer of  $SiO_2$  on both sides of the wafer. In a tube furnace, the low-temperature oxidation process is realized at a temperature of  $600^{\circ}$ C for 40 minutes. Figure 3.9 shows the structure formed after oxidation.  $SiO_2$  passivation effects on the emitter are later discussed in section 4.2.

Figure 3.9. The schematic of the Si wafer after thermal oxidation process.

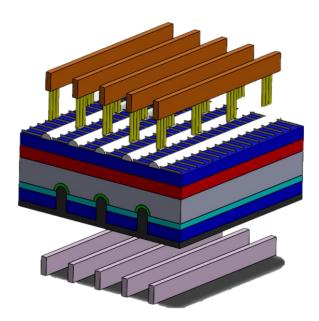

# 3.1.6 Al<sub>2</sub>O<sub>3</sub> Deposition and Activation

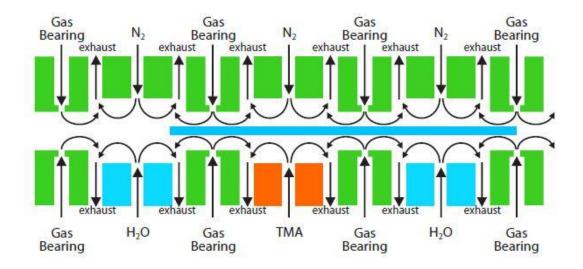

Atomic layer deposition (ALD) is a method to deposit ultra-thin films in a precisely controlled way. Dielectric films are deposited layer by layer. In ODTÜ-GÜNAM facilities, to deposit Al<sub>2</sub>O<sub>3</sub> on Si wafers, Solaytec ALD device is used. It has already been discussed that with the help of the p-n junction, electrons and holes are effectively separated from each other. At the rear side of the cell, holes are the majority carriers and the existence of electrons in that region will cause recombination. A dielectric layer with a negative fixed charge density is necessary to repel electrons from the rear surface. In Figure 3.8, it is shown that the Al<sub>2</sub>O<sub>3</sub> layer has high negative fixed charge density. The mechanism of the deposition is shown in Figure 3.10. During the deposition, the wafer goes forward and backward repeatedly. Trimethylaluminum (TMA) is used as an Aluminum (Al) precursor and liquid DI water is used as an oxygen (O) precursor. When the wafer's rear side reaches the TMA processing compartment, a mono layer is formed on the surface. After that, the wafer moves and reaches the H<sub>2</sub>O processing compartment. A chemical reaction between H<sub>2</sub>O and the monolayer formed by TMA is realized. The product of this reaction is the requested Al<sub>2</sub>O<sub>3</sub> dielectric layer. The repetition number of this process determines the thickness of the layer, or in other words, the number of monolayers determines the thickness.

Figure 3.10. The schematic of the deposition of stoichiometric Al<sub>2</sub>O<sub>3</sub>

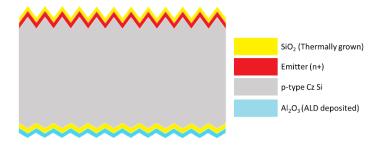

The deposited  $Al_2O_3$  layer is not an active passivation layer. Also, Hydrogen (H) in the layer can cause blistering which leads to the degradation of the passivation [27]. Therefore, an activation annealing process is applied in a tube furnace. In ODTÜ-GÜNAM, this annealing process is applied at 425°C for 15 minutes under  $N_2$  ambient and during the annealing process, the layer is activated and degassed. The structure after the deposition of the  $Al_2O_3$  layer is illustrated in Figure 3.11.

Figure 3.11. The schematic of the Si wafer after Al<sub>2</sub>O<sub>3</sub> deposition.

# 3.1.7 ARC and Capping Layer Deposition

For the p-type rear surface passivation,  $SiO_2$  and  $Al_2O_3$  provide chemical passivation and field-effect passivation, respectively. To create field-effect passivation on the front side and enhance the chemical passivation effects of  $SiO_2$ , a plasma-enhanced chemical vapor deposition (PECVD) grown silicon nitride ( $SiN_x$ ) layer is used. In Figure 3.8, it is shown that the  $SiN_x$  layer has positive fixed charge density and the amount of the fixed charge depends on the stoichiometry of the layer. Also, the  $SiN_x$  layer act as an anti-reflective coating (ARC).

Figure 3.12. Standard Solar Spectra for space and terrestrial use.

The spectrum of the sunlight is shown in Figure 3.12. The peak of the spectrum is around 600 nm, which means that the maximum intensity of sunlight coming from the sun has a wavelength of around 600 nm. To absorb maximum sunlight from this portion of the spectrum; refractive index, stoichiometry and the thickness of the layer should be optimized.

Another SiNx layer is optimized for the rear side of the wafer. At the front side, the main goals for the layer are passivating the n+ emitter and absorbing sunlight as much as possible. However, at the rear side, the  $SiN_x$  layer is used as a capping layer for  $Al_2O_3$  and a back reflector for the non-absorbed light. The  $Al_2O_3$  layer is an ultrathin layer and is sensitive to degradation during the contact firing process.  $SiN_x$

layer also acts as an H source and improves the passivation quality at the rear side. In addition, the bandgap of Si is 1.12 eV and Si can absorb sunlight with a lower wavelength than 1100 nm. Especially, after the 950 nm wavelength, the absorption coefficient is reduced dramatically and the 950-1100 nm portion of the spectrum can be absorbed closer to the rear surface. If the light is not absorbed, with an optimized  $SiN_x$  layer, light can be reflected back into Si and have a second chance to be absorbed. The structure formed after the deposition of the  $SiN_x$  layers is illustrated in Figure 3.13.

Figure 3.13. The schematic of the Si wafer after SiNx deposition.

## 3.1.8 Laser Ablation for Local Contact Opening

For some solar cells like IBC, n-PERT or TOPCon, the back surface field or front surface field is formed before the passivation layers' deposition; generally, P or B diffusions are preferred. For PERC cells, Al is used as BSF due to its low cost and simplicity. However, unlike standard Al-BSF solar cells, the rear side of the PERC solar cell is aimed to be passivated because BSF regions created with Al are highly recombinative. However, the Al paste used to form BSF regions is not able to diffuse through the deposited SiNx layer. Therefore, local openings on the SiNx layer at the rear side are required. To do that, a laser process so-called laser ablation is applied on the rear side. These openings are called as laser contact opening (LCO) and after the metallization/firing process, Al paste fills these LCOs and create Si-Al alloys which help the diffusion of Al atoms into Si. The created structure at the end of the laser ablation process is shown in Figure 3.14.

Figure 3.14. The schematic of the Si wafer after LCO.

#### 3.1.9 Contact Formation

Figure 3.14 illustrate the final structure before the contact formation. When the light comes, it will excite an electron and create electron-hole pair. Due to p-n junction, electrons and holes can be separated from each other (electrons gathered on the emitter side, holes gathered on the bulk) and passivation of both surfaces will help increase the carriers' lifetime. Now, it is required to collect carriers via metal contacts to send them into an external circuit.

In the emitter region, an Ag paste with a firing-through capability collects electrons on the front side. Fire through means that the paste can diffuse through the SiNx layer and get direct contact with the emitter. For the rear side, Al paste is used to form BSF regions and contact. First, Al paste is screen printed on the rear side and went into the dryer. After that, front-side screen-printing metallization is done by a silver paste with an optimized finger and busbar numbers and then goes into the dryer. The structure formed after the metallization process is shown in Figure 3.15.

Figure 3.15. The schematic of the Si wafer after metallization.

After the metallization process, a fast-firing process is applied to the wafers to complete the contact formation and activation of the passivation layers. Before the firing process, Ag paste is just printed and has no contact with the emitter region and Al atoms at the LCO have not formed a BSF region yet. The wafers are placed on the belt, constantly moving at a defined speed. The firing furnace has six different zones with different temperatures to create a suitable temperature profile. The firing process bonds silver to Si at the front and forms BSF regions at the rear side with the help of Si-Al alloys. Al paste fills these LCOs and creates Si-Al alloys which help the diffusion of Al atoms into Si. Figure 3.16 illustrates an SEM image of the formed Al-BSF region.

Figure 3.16. SEM image of the LCO after contact formation [28].

The PERC cell fabrication process is completed at the end of the firing process. After the firing process, cells were characterized by current-voltage (I-V) measurements with a class AAA solar simulator. The complete structure of the cell is shown in Figure 3.17.

Figure 3.17. The schematic of the Si solar cell after contact formation.

# 3.2 Lifetime Samples

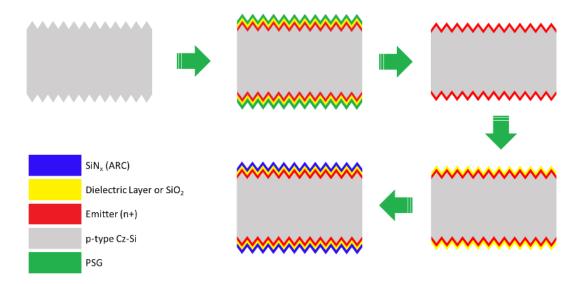

This section gives information about the process flow for lifetime samples. Lifetime samples are necessary to extract the  $J_{0,e}$ , bulk lifetime ( $\tau_{bulk}$ ) and implied open circuit voltage ( $iV_{oc}$ ). For the symmetrical emitter samples, the different POCl<sub>3</sub> diffusion process is applied to the wafers after texturing and cleaning processes. However, instead of an SSE process, the rear side emitter is kept and only HF dipping is applied on the wafers after the diffusion process to remove PSG/SiO<sub>2</sub> on the surfaces. Then, the passivation layers are deposited on both sides of the wafer. After that, wafers are laser-cut into nine pieces by a laser marker for fast-firing process optimizations. The schematic of the fabrication of the lifetime samples is illustrated in Figure 3.18.

Figure 3.18. The schematic of the fabrication of symmetrical emitter samples

## 3.3 Measurement Methods

## 3.3.1 4-Point-Probe

L.B. Valdes proposed the method in 1954, aiming to measure the resistivity of both sides of the p-n junction [29]. Using a 4-point-probe (4PP), the resistivity of different layers and bulk semiconductor materials can be measured [30].

Figure 3.19. The schematic of 4PP measurement

In Figure 3.19, the working principles of a four-point probe are shown. Current (I) flows through the outer probes, while the inner probes measure the floating potential (V). During the optimization studies, PVTOOLS TLM-SCAN four-point probe is used after doping to measure sheet resistances of emitters. The samples are p-type Cz-Si wafers with a size of 156.75 mm x 156.75 mm. Measurements are taken from 25 different points on every sample to determine the uniformity of the diffusion process. The non-uniformity of the wafers is specified with a standard deviation (±).

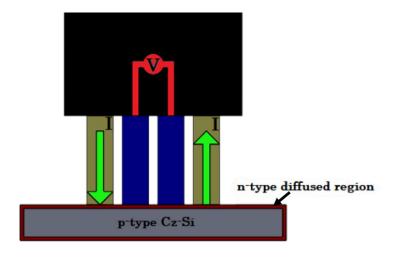

# 3.3.2 Electrochemical Capacitance-Voltage

The electrochemical capacitance-voltage (ECV) method is widely used to measure the active dopant profile of specimens. After every doping process, Wafer Profiler CVP21 was used for the ECV measurements. The schematic of the ECV measurement is shown in Figure 3.20. Ammonium bifluoride (NH<sub>4</sub>HF<sub>2</sub>) is an electrolyte that does not directly etch the Si under no electricity conditions. For ptype surfaces, holes are the majority carriers which is essential because to etch Si; four valence electrons recombine with holes and the remaining positively charged Si+4 core atom is then diffused through the negatively charged electrolyte. However, in the case of n-type Si, holes are minority carriers. Therefore, n-type surfaces cannot be etched in the same way as p-type surfaces. Two possible solutions exist. First, etch voltage can be increased so that the Schottky interface goes into a breakdown condition, creating a very huge etch current. However, the user cannot control this voltage, and the company does not recommend this method. Second, due to the lack of holes in the n-type semiconductors, electrons are excited by photons. With the help of the Schottky depletion layer on the semiconductor surface, holes move through the semiconductor surface and electrons move through the semiconductor bulk. Then, created holes can release valency electrons by recombination. Like in the p-type material, if all the valency electrons can be removed, then the positively charged core Si atom can diffuse through electrolyte fluid.

The user manual provided by the company and other studies in the literature suggest that sheet resistance calculated by ECV should be corrected by 4PP. This can be done by calibrating the device with a bulk wafer that has the same surface morphology as real samples to find out the surface roughness or changing the surface roughness value to get the same sheet resistance value with 4PP [31], [32].

Figure 3.20. The schematic of ECV measurement

## 3.3.3 Sinton WCT120TS Lifetime Tester

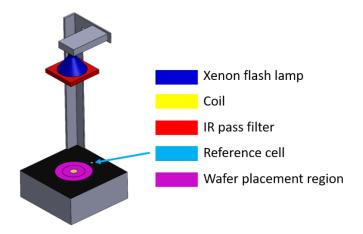

Sinton WCT-120 and Sinton WCT-120TS are used for quasi-steady-state photoconductance (QSSPC) measurements [33]. With the help of an RF coil and an IR pass-filtered xenon flash lamp, the instrument measures the samples' effective carrier lifetime ( $\tau_{\rm eff}$ ). The instrument is an ideal and accepted device in the literature

to measure dopant diffusion and passivation quality of that diffused region. The schematic of the Sinton WCT-120TS device can be seen in Figure 3.21.

Figure 3.21. The schematic of Sinton WCT-120TS device

Carrier lifetime is the time between the generation and the recombination of the minority carrier.  $\tau$ eff, which is measured by the photoconductance method, represents carrier lifetime affected by all recombination channels existing in the wafer. Since surfaces are passivated during the high-temperature phosphorus diffusion process by the PSG layer, measured  $\tau_{\rm eff}$  after the diffusion step gives a strong idea about the final cell lifetime. If both the front and the rear surface of the wafer are diffused, then the following expression shows the effective lifetime of the sample:

$$\frac{1}{\tau_{eff}} - \frac{1}{\tau_{Auger}} = \frac{1}{\tau_{SRH}} + \left[ J_{0,e(front)} + J_{0,e(rear)} \right] \left( \frac{N_A + \Delta n}{qW n_i^2} \right)$$

Eq.17

Here, elementary charge (q) equals 1.602E-19 C and  $n_i$  equals 8.6E9 cm<sup>-3</sup> at 25°C. The user must know that W represents wafer thickness and  $N_A$  is the number of acceptor atoms, which in this case is base doping.  $\Delta n$  is the injection level at which the device provides the data.  $\tau_{Auger}$  and  $\tau_{SRH}$  are Auger recombination lifetime and SRH recombination lifetime, respectfully.  $J_{0,e(front)}$  and  $J_{0,e(rear)}$  represent the emitter's saturation current density, which characterizes the emitter region. Auger recombination is the dominant recombination channel in the emitter region and  $\tau_{Auger}$

strongly depends on the  $\Delta n$ . The software provides the plot of inverse auger corrected lifetime vs. injection level, which gives the information of  $J_{0,e}$ .

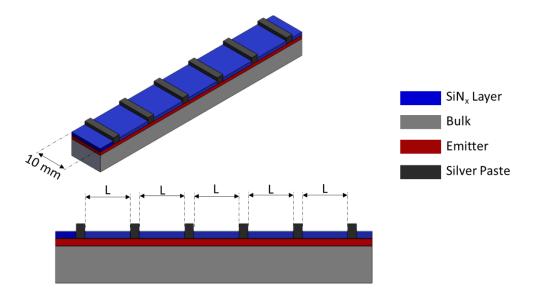

## 3.3.4 Transfer Length Method (TLM)

The transfer length method (TLM) is widely used to calculate the contact resistivity between metal and semiconductor ohmic structures. In the case of industrial PERC cells, instead of a spreading structure, finished solar cells with equidistant contacts are cut into stripes to isolate the fingers. The method proposes to measure the voltage drop between all the permutations for the array of contacts. Then, by using the least squares approach, a linear fit is obtained and the sheet resistance of the semiconductor (R<sub>sheet</sub>) is the slope of the fit and the contact resistance (R<sub>c</sub>) is the interception of the fit and the resistance axis[34]. In this study, the PVTOOLS TLM-SCAN device is used to measure contact resistivity and the schematic of equidistant TLM stripe structure can be seen in Figure 3.22.

Figure 3.22. The schematic of a TLM stripe

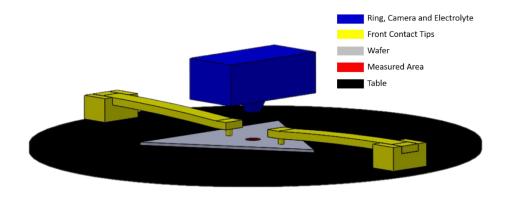

### 3.3.5 IV Measurement

The current and voltage (I-V) properties of a photovoltaic (PV) cell show the cell's solar energy conversion capacity and efficiency. One can determine the cell's output performance by knowing its I-V characteristics. Some important parameters should be known when characterizing the cell performance. The first one is  $V_{oc}$ , which is the voltage across the cell when no electrical load is applied. The second parameter is  $I_{sc}$ , which is the current value when the voltage across the cell is zero. The third parameter is the FF, which shows the recombination losses at the junction and resistive losses. The slope of the curve at  $J_{sc}$  gives information about the shunt resistance and the slope of the curve at  $V_{oc}$  provides information about the series resistances. The curve at  $J_{sc}$  should be as horizontal and the curve at the  $V_{oc}$  should be as vertical as possible for an efficient solar cell.

After designed PERC cells were produced, Mondragon Assembly Photovoltaic Cell Tester and Sorter was used. The schematic of the measurement is shown in Figure 3.23. During the measurement, probes contact the cell from the front busbars and rear Al metallized area.

Figure 3.23. The schematic of IV measurement

#### **CHAPTER 4**

#### RESULTS AND DISCUSSION

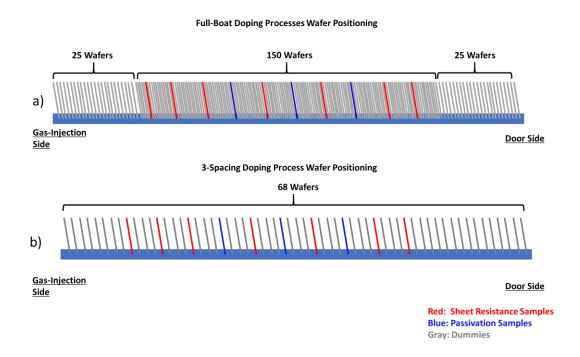

## 4.1 Optimization of the Process Conditions

The resulting emitter profile depends on parameters like temperature, duration, gas ratios, configuration and position of the wafers. The amount of P in the PSG layer depends on gas ratios between POCl<sub>3</sub> carried by N<sub>2</sub> and O<sub>2</sub> while increasing temperature or duration helps more P atoms diffuse from PSG to Si wafer and obtain deeper profiles. Also, the configuration and positioning of the wafers affect the flow in the tube, so it is critical to optimize the positions and number of wafers used in the process. The reason is that in atmospheric diffusion furnaces, uniformity and amount of dopant diffused into the wafer highly depend on the amount of wafer and the flow in the tube. DG Plasma diffusion furnace has a boat with 270 slots, which means 270 wafers can be processed symmetrically or 540 wafers can be processed single side if two wafers are put on the same slot back-to-back. Due to the lack of dummy wafers during the experiments, the so-called full-boat doping processes in Figure 4.1a are held on with 200 wafers. In addition, the so-called 3-Spacing doping processes in Figure 4.1b with 68 wafers are carried out to realize the diffusion process with fewer samples. In the figure, red wafers represent the samples used for 4PP measurements while blue samples are used for lifetime measurements. In

addition, gray wafers represent the dummy wafers used to fill the entire boat to provide uniform gas flow.